ムーアの法則が限界に達しつつあるなか、チップメーカーは新たなテクノロジに目を向け、プロセッサの高パフォーマンス化を図っている。

ムーアの法則は限界に達しつつあるが、チップメーカーはその歩みを緩めようとしていない。

チップメーカーとしての道のりは決して平坦ではない。しかしこの50年の間はほとんど、比較的ストレートな手段を採ることで進んできた。トランジスタの大きさをどんどん小さくし、高密度化を図ることで、処理パフォーマンスの向上(そして消費電力の削減)や、新機能の追加を達成できていたのだ。こういった進歩の道は(まだ)閉ざされたわけではないが、新たな節目節目に到達するまでに多大な時間を要するようになるとともに、コストも上昇してきている。その一方で、高パフォーマンス化や電力消費量の削減という見返りはどんどん小さくなってきている。

このためチップメーカーは、並列化(コア数の増加)や、電源管理機能の向上、メモリ容量と帯域幅の拡大、内部接続の高速化、オフチップアクセラレータの採用を通じて費用対効果に優れた新たな道を模索している。こうしたトレンドは、メーカーのプロセッサに関する最近の発表からも見て取れる。

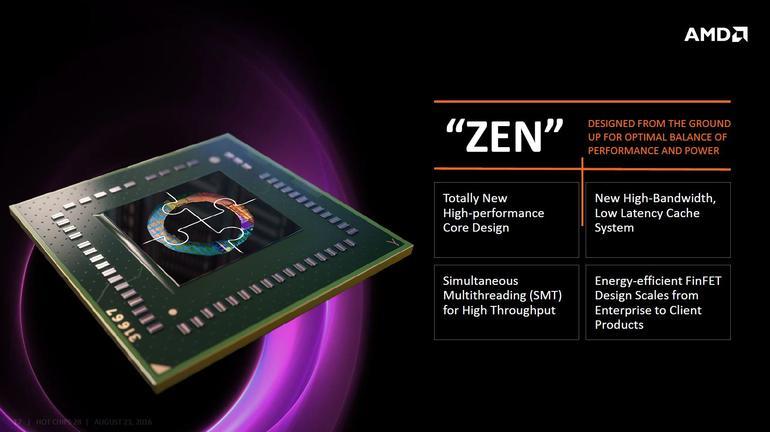

「Zen」で復活を目指すAMD

例を挙げてみよう。カリフォルニア州クパチーノで米国時間8月21~23日に開催されたプロセッサ関連のカンファレンス「Hot Chips 28」では、Advanced Micro Devices(AMD)の「Zen」マイクロアーキテクチャが際立っていた。このまったく新たな設計に基づくマイクロアーキテクチャによって、同社のプロセッサはIntelの最速プロセッサに再び対抗できるようになるとうたわれている。AMDは、同じ消費電力で1クロックあたり40%多くの命令を実行できるようにするのがその目標だと語っている。またZenは、薄型軽量のノートPCから高性能サーバに至るまでのスケーラビリティを備えており、「Puma」マイクロアーキテクチャに基づく低消費電力プラットフォームの出番をなくしている。これはリソースに制約がある同社にとって重要な戦略と言えるだろう。

提供:AMD

現行の「Bulldozer」マイクロアーキテクチャでは、2つの整数演算コアが命令のフェッチとデコードを行うフロントエンドと、浮動小数点演算ユニットを共有している。これは、単一のダイ上により多くの整数演算コアを搭載するためのスペースを確保するという考え方に立脚した設計だが、パフォーマンス上のボトルネックも同時に生み出していた。一方、Zenのコアはリソースを共有しない。各コアはデュアルスケジューラ(整数演算処理向けと浮動小数点演算処理向け)を有しており、独自の浮動小数点演算ユニットも備えている。

さらに重要な点として、Zenは1コアあたり2つのスレッドを実行できる、AMD初となる正真正銘の同時マルチスレッディング(SMT)をサポートしている。またこの新デザインは、マイクロコードのキャッシュ機能や、より優れた分岐予測機能など、パフォーマンス向上につながる多くの特長も備えている。そのうえで、数多くの新命令もサポートしている。こういった新命令の一部は既に「Intel Core」プロセッサで採用されているが、AMD独自のものもある。とはいえ、その全容は明らかにされていない。