Intelは先ごろ、第2世代「Xeon Phi」プロセッサについて、いくつかの新しい詳細を発表し、初めて公の場でデモを披露した。「Knights Landing」として知られるこのチップは、あらゆる意味でビッグである。Intelの最新の14ナノメートルプロセスで製造される同チップは、80億個ものトランジスタを搭載するほか、大容量のオンパッケージメモリを搭載し、現行Xeon Phiの3倍のパフォーマンスを提供すると謳っている。

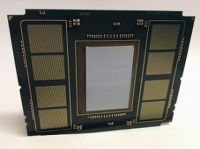

「Knights Landing」Xeon Phiは複数の積層メモリに囲まれた1つの大型チップだ。

提供: Intel

「Many Integrated Core」(MIC)アーキテクチャをベースとするXeon Phiは、Intelのハイパフォーマンスコンピューティングプラットフォームの一部だ。大型で高速なコアを使ってコア数をより少なく済ませた「Xeon E7」やIBMの「POWER」、Oracleの「SPARC」と異なり、Xeon Phiは小型コアを多数使って、金融、石油とガスの採掘用の地殻構造画像処理、生命科学、気象シミュレーション、映像符号化など、さまざまな分野で高度な並列ジョブを処理できるようにする。

現行の22ナノメートルバージョン(開発コード名:「Knights Corner」)は、最大61個の小型コア(計244スレッド)を搭載するコプロセッサで、「Xeon E5」サーバプロセッサと組み合わせて使用される。競合製品は、スーパーコンピュータやワークステーションで使われるNVIDIAやAMDのGPUアクセラレータだ。

Knights Landingは大幅な改良が行われた製品だ。Supercomputing Conference 2013で、IntelはKnights Landingがホストプロセッサとしての役割を備えており、コプロセッサとして機能するだけでなく、単体でOSやアプリケーションを実行する能力も持つことを明かした。2014年のInternational Supercomputing Conferenceでは、同社は同チップの設計について、新しいメモリや予想されるパフォーマンスなど、さらなる詳細を公表した。そして、先週発表された情報により、Intelがそれほど大きなパフォーマンス向上をどのように実現するつもりなのかが少し明らかになった。

Knights Landingの心臓部にあるのは、マイクロサーバやストレージ向け(開発コード名:「Avoton」)、およびネットワーキング向け(開発コード名:「Rangeley」)の「Atom C2000」シリーズプロセッサで使われた「Silvermont」コアを大幅に改造したバージョンだ。Knightsバージョンのアウトオブオーダーのパイプラインは2倍の深さで(一般に、パイプラインが深ければ深いほど、言い換えれば、命令の実行のステージが多ければ多いほど、一定時間内により多くのことを完了できる)、各コアは、浮動小数点演算用の大容量化されたL1キャッシュメモリと512ビットのAVXベクトルユニットを備える。

コアはタイル状に配置される。それぞれのタイルは、2個のコアと共有L2キャッシュ、そして、まとまった網状のネットワークでタイルを接続するハブを備える。Intelが先週、デモを披露したチップは、30個のタイル、つまり60コア/240 スレッド(1個の物理コアにつき4スレッド)の処理性能を備えていたが、同社によると、完成バージョンには60個を超えるコアが搭載されるという。

もう1つの重要なニュースが、メモリアーキテクチャだ。キャッシュの増強に加えて、チップパッケージは、同社が「ニアメモリ(Near Memory)」と呼ぶ2Gバイトの積層DRAMを8個、計16Gバイトのメモリを搭載している。これは、Micronの「Hybrid Memory Cube」の一種のように見える。Hybrid Memory Cubeは、すべてシリコン貫通電極(TSV)で接続された積層メモリチップと内蔵ロジックチップを使って、より低電力で高密度化と帯域幅増加を実現する。Intelによると、オンパッケージメモリは、ハイパフォーマンスコンピューティングの標準的なメモリ帯域幅テストで、DDR4メモリの5倍のパフォーマンスを発揮するという。Knights Landingも最大384GバイトのDDR4「ファーメモリ(Far Memory)」に接続可能な従来型メモリチャネルを6個備える。

こうしたすべての要素(より高度なプロセスと新しいコア設計、キャッシュの増量、斬新なメモリアーキテクチャ)の結果として、パフォーマンスが大幅に向上する。Intelによると、CPUコア自体は、固定小数点整数演算で現行Knights Corner Xeon PhiのCPUコアの3倍のパフォーマンスを発揮するという。チップレベルでも、Knights Landingは約3倍のパフォーマンスを発揮する。Knights Cornerは倍精度で1テラフロップス(1秒間に1兆回の浮動小数点演算)、単精度で2テラフロップスを少し上回る性能を備えるが、Knights Landingは倍精度で3テラフロップス、単精度で6テラフロップスを実現する。