[画像1: (リンク ») ]

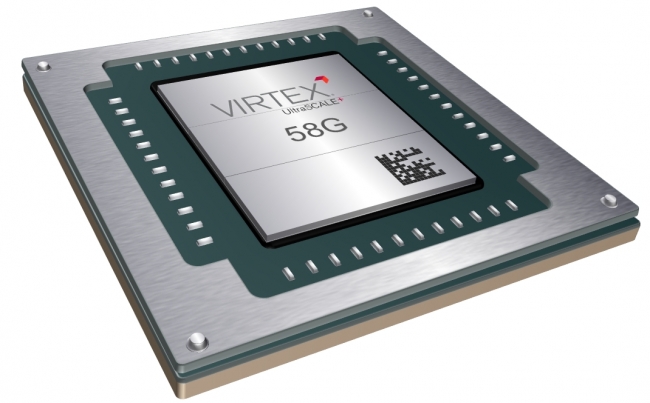

All Programmable 製品のリーディング プロバイダーであるザイリンクス社 (本社 : 米国カリフォルニア州サンノゼ、NASDAQ : XLNX) は 3 月 12 日 (米国時間)、OFC 2018 において、ザイリンクスが主導する光ネットワーク テクノロジを展示すると発表した。ザイリンクスは、光ネットワーク向け電気信号テクノロジとして画期的な 112G PAM4 のデモを FPGA 業界で初めて展示し、ネットワークの未来を紹介するとともに、16nm Virtex(R) UltraScale+™ ポートフォリオへの 58G PAM4 トランシーバーの追加を発表する。

[画像2: (リンク ») ]

クラウド サービス および 5G サービスの開始によるデータ トラフィックの急増は、急拡大するネットワーク内帯域幅要件への対応に課題をもたらしつつある。ルーターおよびスイッチ内のライン カード ポート密度、光伝送規格の進展、光ネットワーク帯域幅のアップデートは、費用対効果の高い方法で継続的に帯域幅要件を満たす上で大きな制約となっている。58G および 112G トランシーバーへの移行は、既存のフットプリントで 400G および 800G+ データ レートを実現するための重要な一歩である。

112G PAM4 テクノロジ デモ - ザイリンクスが定める次世代の性能

ザイリンクスは、速度とスループットへのさらなる要望に応えるため、シングル レーンでの全二重 112 G PAM4 信号通信のデモを実施する。業界の専門家は、次世代の光ネットワークおよびライン カード密度に対応するには、112 Gb/s トランシーバー性能が不可欠であると見なしている。また、顧客からは、ザイリンクスの次世代 7 nm ポートフォリオへの 112G トランシーバー搭載プログラマブル デバイスの追加が期待されている。

Moor Insights & Strategy 社の高性能コンピューティングおよび機械学習担当シニア アナリストであるカール フロイント (Karl Freund) 氏は、「ザイリンクスは長年にわたって、シリアル インターコネクト テクノロジの規格推進に取り組み、性能の限界を押し広げてきました。今回の業界初となる 112G PAM4 デモと 58G PAM4 ソリューションを通じて、顧客がこれらを設計に組み込めるようにするため、引き続きザイリンクスは取り組みを続けています。今回のザイリンクスの発表は、光ネットワークの帯域幅性能に関して継続的に改善を求められるネットワーク アーキテクトにとって、飛躍的な前進となります」と述べている。

58G PAM4 FPGA 新製品 - すぐに設計を開始可能

ハイエンド アプリケーション向けとして最も需要が高い Virtex UltraScale+ デバイス クラスをベースに構築された、新しいザイリンクスのトランシーバー アーキテクチャを利用し、プログラマブル ロジックの柔軟性に 58G PAM4 トランシーバーを組み合わせることで、事実上、既存システムの2倍の帯域幅性能を実現できる。既存の 25G バックプレーン上で動作するこれらのデバイスは、現行システムの寿命と帯域幅を拡大すると同時に、次世代テクノロジへの移行を容易にする。58G トランシーバー搭載の新しいデバイスは、移行を考慮して、現在製造中の既存の Virtex UltraScale+デバイスとフットプリントにおいて互換性を備えている。

クラウド コンピューティング、5G ネットワーク、コア ネットワーク (OTN、イーサネット)、ネットワーク機能仮想化 (NFV) アプリケーションを対象とする、この最新トランシーバー アーキテクチャにより、ベンダー各社は、複雑さを緩和した小型システム設計で、50G、100G、400G ポートおよびテラビット インターフェイスへの拡張を実現できる。

ザイリンクスのコミュニケーション マーケット担当バイス プレジデントであるファハド シャーファイ (Farhad Shafai) は、「ネットワークは、より高速かつより柔軟で、より適応性の高いシステムを実現するために劇的に変化しており、業界は新しいオプティクスと規格がもたらす変化に向けて、態勢を整えつつあります。生産実績を誇るシリコン、高品質を実現してきた実績、オプティクスおよびバックプレーンなどの主要テクノロジの開発におけるエコシステムとともに、ザイリンクスが、柔軟性と適応性の最も高いソリューションを最初に提供できることを光栄に思います」と述べている。

新製品となる 58G PAM4 Virtex UltraScale+ デバイスは、PAM4 トランシーバー、100GE IP ブロックおよび次世代インターコネクトに必要なすべての関連 FEC (フォワード エラー訂正) 機能を備えている。

ザイリンクスは、OFC 2018 のブース #2807 にて、58G および 112G PAM4 のデモを行う。また、ブース #5525 にて開催される OIF (Optical Internetworking Forum) の 56 Gb/s 相互運用性デモに参加する。

ザイリンクスについて

ザイリンクスは、All Programmable FPGA、SoC、MPSoC、RFSoC、3D IC の世界的なリーディング プロバイダーである。ソフトウェア定義でハードウェアが最適化されたアプリケーションを可能にすることによって、クラウド コンピューティング、5G ワイヤレス、エンベデッドビジョンおよびインダストリアル IoT などの分野に飛躍的進歩をもたらす。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

※ザイリンクスの名称およびロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、その他本プレスリリースに記載のブランド名は米国およびその他各国のザイリンクスの登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

■下記のザイリンクス株式会社ウェブサイトもご参照ください。

・トップページ : (リンク »)

・プレスリリース (日本語) : (リンク »)

・このリリースの全文は次の URL を参照のこと :

(リンク »)

プレスリリース提供:PR TIMES (リンク »)

お問い合わせにつきましては発表元企業までお願いいたします。