米Intelは米国時間7月26日、報道機関向けのオンラインイベント「Intel Accelerated」を開催。同社半導体の製造プロセスとパッケージング技術に焦点を当てて、今後数年のロードマップを明らかにした。

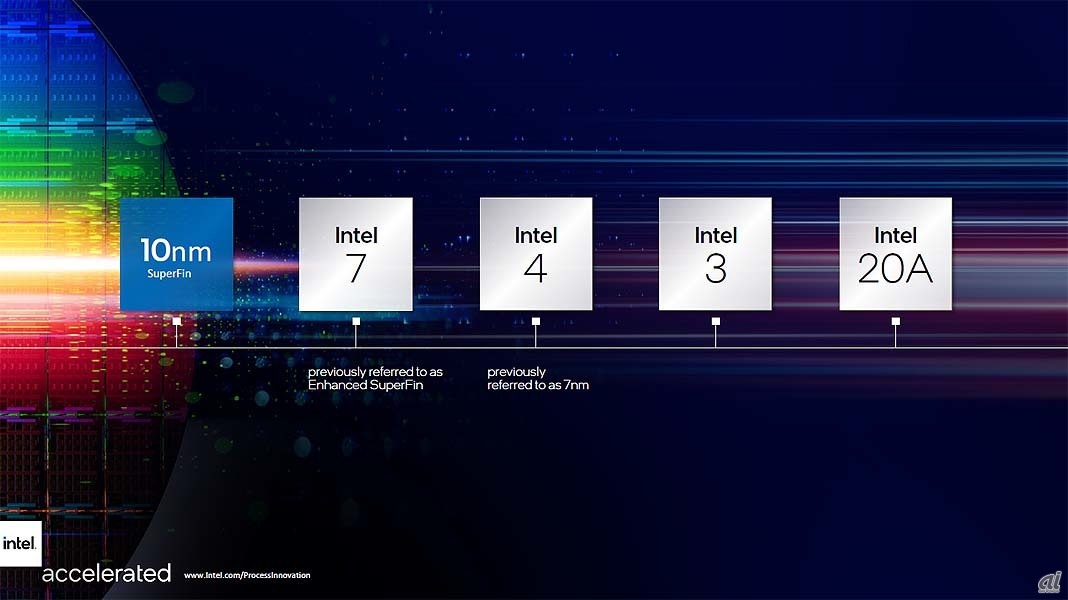

製造プロセスについては、従来の“nm”(ナノメートル)を単位とした呼び方を止め、新たに単位を明示しないバージョン番号のような呼び方に整理された。ただし、使われている数字字体は従来のnm表記で使われるものとおおよそ同一である。この名称変更に関しては、簡単に説明すると「歴史的には特定のトランジスターの長さなどを示す数字が使われており、Intelではこの慣習にずっと従ってきたが、一方他社は必ずしも特定の物理的な長さを示す数字とは限らないものを使用している」ことから、同社でも「主要な幾つかの指標に基づいた改善度合いを見て数字を小さくする」方針に転じたという。

製造プロセス技術のロードマップ

端的に言えば、「Intel 7」から「Intel 4」に世代が変わった場合、トランジスターの物理的なサイズが7nmから4nmに縮小されたことを意味するわけではないが、性能や消費電力、専有面積などを含むいろいろな値を総合的に判断して新世代を特徴付ける数字を与える、ということになっている。また、現状この数字が“1”に近づいていることを踏まえて、同社では新たなネーミングとして“20A”を打ち出し、この世代以降を「The Angstrom Era(オングストローム世代)」と呼んでいる。

オングストロームは長さの単位として使われていたもので、定義が幾つかあるものの、最も基本的な定義では“1A=0.1nm”となるので、20Aとは従来の表記では2nmと同じ意味になると考えてよいだろう。ただし、前述の通り厳密な意味で何かの長さを示す数字ということではないため、世代間の移行は実際には新たな技術要素が投入されて改善が行われることを意味すると考えてよい。オングストローム世代の幕開けと位置付けられる20Aでは、「RibbonFET」と「PowerVia」という新技術が導入される予定となっており、この2つの技術こそが新たな時代を切り拓く大きなイノベーションとして位置付けられている形だ。

Intel 7は、これまで「10nm Enhanced SuperFIN」と呼ばれていた世代で、他社が7nmプロセスと呼んでいる世代に対して周回遅れ的なイメージを持たれてしまっていたのに対して、名称変更によって事実上の同等世代であるとアピールする狙いだと考えて良さそうだ。FinFETトランジスターの最適化によって、現行の「10nm SuperFIN」との比較で消費電力量当たりのパフォーマンスが10~15%向上するという。

2021年に生産開始予定のクライアント向けCPU「Alder Lake」(開発コード名)や2022年第1四半期に生産開始予定のデータセンター向けCPU「Sapphire Rapids」(同)がIntel 7で製造される予定だ。次のIntel 4は従来“7nm”とされていたプロセスで、ここでも1世代分先の名称に付け直されている。

技術面での特徴としては、同社として初となる全面的なEUV(Extreme Ultra-Violet、極端紫外線)リソグラフィーを採用する点だ。EUV露光技術を主導するオランダのASMLに加え、EUVマルチビームマスクライターの主要サプライヤーとしてIMS Nanofabricaitonの名前が挙がっている。クライアント向けCPU「Meteor Lake」(開発コード名)とデータセンター向けCPU「Granite Rapids」(同、いずれも2023年出荷開始予定)の生産を2022年後半から開始する予定だ。

Intel 3は、FinFETやEUVの改良によって性能向上を実現するとされる。そして、前述の通りIntel 20AではRibbonFETとPowerViaが導入される。RibbonFETは、ゲートの中央部分にフィンを貫通させてフィンの4面を覆う形にし、さらにフィンを垂直方向に積み上げることで専有面積の削減も狙うトランジスター構造だ。また、PowerViaは電源配線をシリコンウエハの裏側から行うというもの。これらの技術をさらに改良する予定の次世代「Intel 18A」の開発も2025年初頭を目標に既に開始されているという。

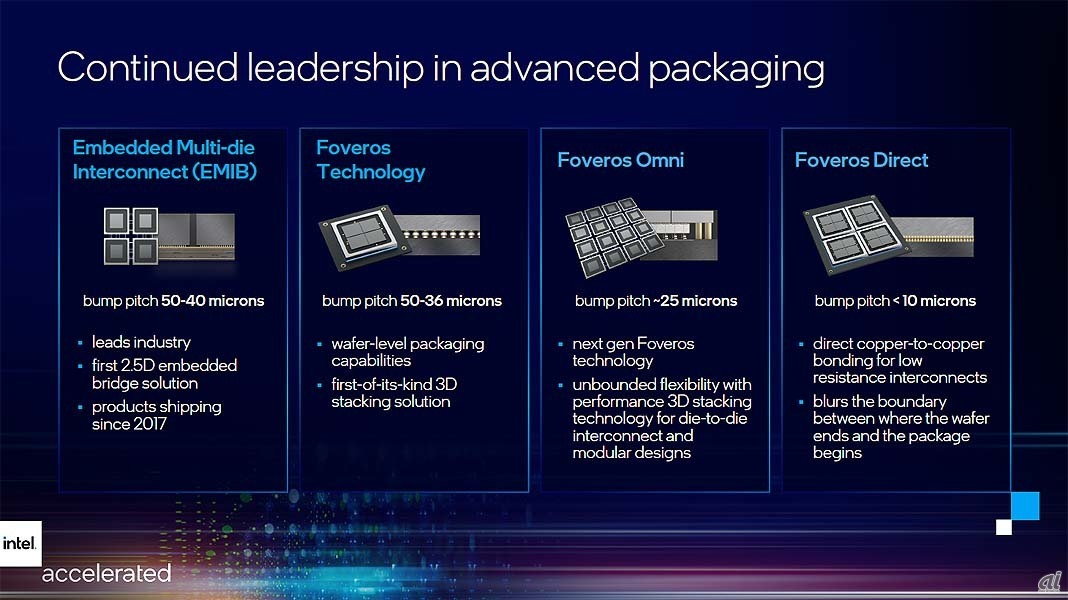

パッケージング技術については、「EMIB」(Embeddeed Multi-Die Interconnect Bridge)、ウエハレベルでの3Dスタッキング技術である「Foveros」「Foveros Omni」「Foveros Direct」などの強化の予定が紹介された。

パッケージング技術の概要

イベント冒頭で全体的な戦略の説明を行った同社 最高経営責任者(CEO)のPat Gelsinger氏は、3月に発表されたIDM 2.0戦略を改めて振り返るとともに、「世界クラスのファウンドリー」を実現するために米国内(アリゾナおよびニューメキシコ)で巨額の投資を行っていることを紹介した。そして今回公表された製造プロセス技術とパッケージング技術のロードマップは、同社のファウンドリー事業と組み合わせた場合に顧客に大きなメリットをもたらすことになる。

同社は10nmプロセスへの移行でつまづき、数年にわたる低迷を経験したが、そうはいっても同社が半導体製造技術に関して世界トップクラスの研究開発能力を有することは間違いない。その成果として今回発表された新しい製造プロセス技術やパッケージング技術は、ファウンドリーとして同社を利用する顧客企業にも提供されることになるため、ファウンドリー事業に関しても競合に対するアドバンテージとして魅力を持つことになる。実際、携帯電話やスマートフォンのプロセッサーメーカーとして同社の競合とも位置付けられるQualcommがIntel 20A世代で同社のファウンドリーサービスを利用すると発表されている。従来は考えにくかった形の協業が実現しており、まさに時代が変わりつつあることが実感される。

Intel CEOのPat Gelsinger氏

イベントの中でGelsinger氏が何度か繰り返し強調したメッセージが「Intel is Back.」であった。一時期同社が低迷していたことを認めつつ、新たな戦略のもとで同社が再び力強く歩み始めることを明確に宣言したものだろう。ただ、一方で懸念材料としては、同社自身がどう考えているかはともかくとして、現在の同社の戦略には米中対立が背景にあることが否定できない点だ。

現在の半導体製造拠点(ファウンドリー)が台湾やアジア諸国に集中していることに対し、米国内や欧州圏で十分な生産能力を確保しようとする同社のファウンドリー戦略は、中国が半導体供給に支配的な影響力を行使することで、米国や西側諸国に対する“武器”とする可能性を米国政府が危惧していることを反映していることはまず間違いないだろう。単なる技術開発競争/ビジネス面での競争にとどまらず、政治的な対立構図が鮮明なることはリスク要因として意識しておく必要がありそうだ。

とはいえ、Gelsinger氏がCEOとして同社に復帰したことで同社が自信を取り戻し、急激にさまざまな状況が好転しつつあるように見えるのは業界全体にとっても好材料といえるだろう。今回発表されたロードマップが予定通り実現されていくことに期待したい。