富士通の「SPARC M12」は、同社が開発した最新プロセッサ「SPARC64 XII」を採用したUNIXサーバだ。CPUコア性能が従来機「SPARC M10」の最大2.5倍に高められ世界最高値を記録している。そればかりか、メインフレームクラスの信頼性が確保され、また、ビッグデータのリアルタイム分析でも圧倒的な性能を発揮する。この抜群の性能は、いかなる開発努力とノウハウ、そして創意工夫によって実現されたのか──。その一端をとらえるべく、SPARC M12開発に携わった富士通 アドバンストシステム開発本部 プロセッサ開発統括部第一技術部部長の山下英男氏と坂下聡太氏、そして、実装技術開発統括部の田和文博氏に話を聞いた。田和氏は、SPARC M12の高密度実装を可能にした独創的な冷却技術「Vapor and Liquid Loop Cooling(VLLC)」の開発で中心的な役割を果たした人だ。

SPARCを熟知しているからこそブレークスルーが実現できる

―― 早速、SPARC64 XII開発の話をお聞きしたいのですが、その前に、SPARCアーキテクチャを採用し続けている理由について教えてください。

富士通株式会社

アドバンストシステム開発本部

プロセッサ開発統括部

第一技術部 坂下聡太氏

坂下まず第一に、SPARCは、独立非営利組織「SPARCインターナショナル」によって管理されている、オープンで、設計依存で仕様拡張可能な余地があるアーキテクチャだからです。さらに富士通は長年にわたり、SPARCアーキテクチャのプロセッサを開発しており、その仕様を熟知しています。ですから、自分たちの経験、ノウハウ、アイデアを活かして仕様の拡張を行い、かなり思い切った強化を行うことができます。例えば、SPARC64 XIIでは、スーパーコンピュータのプロセッサ「SPARC64 VIIIfx」で取り入れたハイパフォーマンスコンピューティング(HPC)向けの拡張仕様「HPC-ACE(High Performance Computing Arithmetic Computational Extension:拡張命令セットアーキテクチャ)」を引き継がせ、そのうえでSPARC64 X/XIIの特長的な機能である「ソフトウェア・オン・チップ」を実現するための新規命令を実装しました。また、HPC-ACEの実装に当たり、SPARC64 XIIの浮動小数点レジスタの本数を共通仕様である「SPARC V9」アーキテクチャの4倍である128本にまで拡張し、メモリへのデータ退避/復元の回数を大幅に削減しました。こうしたSPARCアーキテクチャの拡張・強化によって、SPARC M12は、性能面で他社製サーバを凌駕する、大きなブレークスルーが引き起こせたと確信しています。

その一方で、SPARCプロセッサは長年にわたり数多くのお客様にご利用いただいているので、その上で動作するソフトウェア資産もしっかりと保護していかなければなりません。SPARCアーキテクチャをしっかりと守りつつ、独自の新しい世界を切り開いていくことが大切なのです。つまりSPARCアーキテクチャを採用し続けていることで、プロセッサのレベルから他のシステムベンダーとの差別化が図れるということです。

―― そのほかに、SPARCプロセッサの自社開発がもたらすメリットは何かありますか。

坂下当社は、SPARCプロセッサのみならず、SPARC M12のハードウェア全体やファームも開発しています。そのため、万が一、お客様が利用するSPARC M12に問題が発生しても、開発チームが早急に調査・分析に当たり、問題原因を突き止めることが可能です。 外部から仕入れた部品をただ組み立てているだけでは、このような障害対応は成しえないのです。

「コア性能で世界一」に挑んで

――SPARC64 XIIプロセッサの開発に当たり、最大の挑戦は何だったのでしょうか。

坂下我々の目標の一つは、「コア性能で世界一」を達成することでした。ただ、コア性能を引き上げようとすればするほど、SPARC64プロセッサの強みの一つと言えるシングルスレッド性能が犠牲になる可能性がありました。そのため、高いシングルスレッド性能の維持とコア性能の向上をどう両立させるかで悩みました。

――そもそもコア性能のジャンプアップにこだわった理由は何なのですか。

富士通株式会社

アドバンストシステム開発本部

プロセッサ開発統括部

第一技術部 部長

山下英男氏

山下お客様のTCO(総所有コスト)を最適化するためです。SPARC M12で使用される主要なソフトウェア製品はコア単位での課金が一般的です。ですから、コア性能を可能な限り向上させて、ジョブあたりに必要とされるコア数をより少なくし、お客様のソフトウェアコスト(ラインセンスコスト)の低減やTCOの最適化につなげたいと考えたのです。

――なるほど。SPARC64 XIIではコア性能が前世代の約2.5倍とお聞きしています。となると、単純に言えば、ソフトウェアのライセンスコストが半分以下に圧縮できる可能性があるわけですね。ところで、この大幅な性能向上をどのようにして実現したのですか。

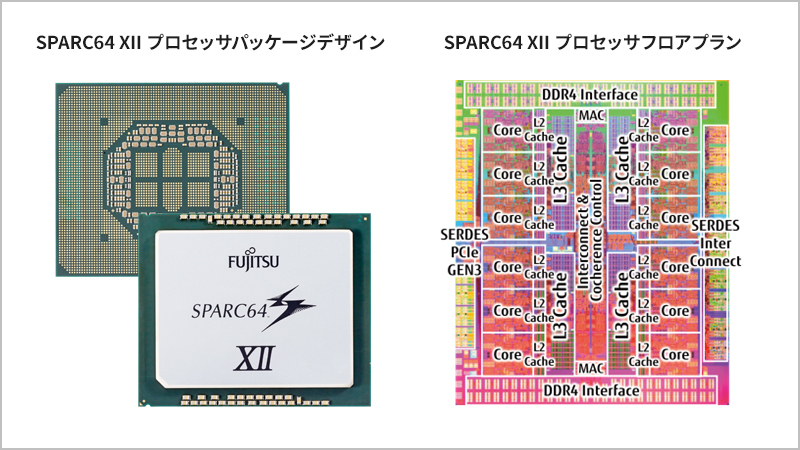

坂下一つは、プロセッサの最大周波数を前世代の3.7 GHzから4.25 GHzに引き上げたことです。またもう一つは、コアあたりのスレッド数を従来の2から8へと4倍に増やしたことです。これらが実現できた理由としては、20nmプロセスの採用で集積度が上がったことと設計上の工夫が挙げられます。

もっとも、コアとしてのスペックが上がれば単純に性能が向上するわけではありません。スレッド数を増やすと回路の増加によって1サイクルの処理が多くなり、周波数向上の妨げになります。その中で、周波数を上げるために単純にパイプライン段数を増やしただけでは、パイプライン処理にバブル(=命令が実行できないステージ)が発生してしまい、逆に性能が落ちてしまう場合もあります。そのような事態に陥らないよう、分岐予測性能の向上やバイパス強化、コア内のリソース使用効率アップなど、マイクロアーキテクチャ(プロセッサの内部構造)に工夫を凝らしました。それが、SPARC64 XII開発における最大のポイントだったと言えます。

図1:SPARC64 XII プロセッサ

図1:SPARC64 XII プロセッサ

※クリックすると拡大画像が見られます

──そうした課題を乗り越えた結果、当初の目標どおりに、「SPECint®_rate2006」ベンチマークにおいて、CPUコアあたりのピーク性能が「IBM Power 8」を抑えて世界トップの座に立ったということですね(2017年11月30日現在)。

坂下ええ、そのとおりです。