数十年もの間、コンピューターチップの性能は、電子回路がどれだけ小さく、密に集積されているかで評価されてきた。ここにきてIntelは、そうしたチップ群をいかに巧みにパッケージングして、より強力な1つのプロセッサーに仕上げるか、という別の評価軸を重要視している。

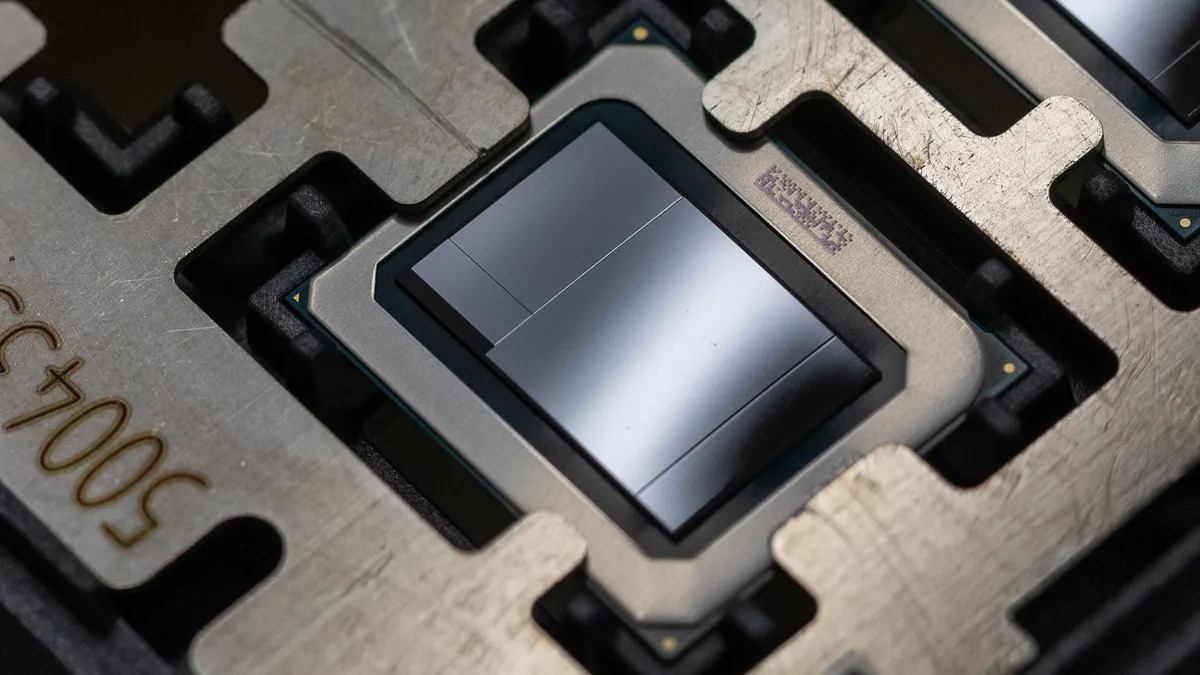

IntelのMeteor Lakeの試作版

提供:Stephen Shankland/CNET

米国時間8月22日に開幕した「Hot Chips」カンファレンスにおいて、Intelの最高経営責任者(CEO)Pat Gelsinger氏は、自社のパッケージング技術について語る予定だ。パッケージング技術は、2つの新しいプロセッサーにとって極めて重要な要素となる。その2つとは、次世代「Core」プロセッサーファミリーで2023年に出荷予定のPC向けプロセッサー「Meteor Lake」と、エクサスケールスーパーコンピューター「Aurora」に搭載されている「Ponte Vecchio」だ。

複数の「チップレット」を接続して1つの大きなプロセッサーにすることができる先端パッケージング技術は、将来のPCをより高速かつ高性能にするためのカギとなる。この先端パッケージング技術は、AMDがトップエンドのPC向けプロセッサー「Ryzen 7 5800X3D」に採用している。Appleも、この技術を用いて2基の「M1 Max」チップを組み合わせ、同社の最も強力な「Mac」向けプロセッサー「M1 Ultra」を構築している。

しかし、このRyzenチップの販売価格は449ドル(6万5300円)で、M1 Ultraを搭載する「Mac Studio」は、M1 Max搭載版よりも2000ドル(28万円)高額だ。IntelのMeteor Lakeは、パッケージング技術をメインストリームPC市場にもたらす製品となる。低調な年でも年間数億台のマシンが売れる同市場への進出は、より高速かつ強力で、なおかつ手頃な価格のコンピューターの登場につながる。

Meteor Lakeはそのパッケージング技術によって「大きな技術革新となるだろう」とReal World TechのアナリストDavid Kanter氏は述べている。

何十年もの間、チップの進化の最先端といえば、その電子回路を小型化することだった。チップメーカーは、フォトリソグラフィーと呼ばれる技術を用いて回路を作製する。これは光のパターンを使って、シリコンウエハー上にトランジスターと呼ばれる極小のオンオフスイッチをエッチングするものだ。トランジスターが小さいほど、設計者はグラフィックスや人工知能(AI)のアクセラレーターなど新たな機能を追加できる。

Intelは、このようなチップレットをパッケージに統合することが、従来のフォトリソグラフィー技術と同様の処理能力の向上をもたらすと考えている。

「パッケージング技術は、プロセス技術そのものと同じくらい重要だというのがわれわれの立場だ」と、IntelのDesign Engineering Groupを率いるBoyd Phelps氏はインタビューで述べている。

Intelは高度なパッケージング技術によって47のチップレットをPonte Vecchioプロセッサーに組み込んでいる

Stephen Shankland/CNET

パッケージング技術は、Intelにとって重要な意味を持つ。同社は、Appleのチップを製造する台湾積体電路製造(TSMC)やサムスンに明け渡した主導的地位の奪還に苦戦している。新しい半導体製造施設に数百億ドル規模を投じているにもかかわらず、直近の四半期決算は「散々たる」ものだったと、TechInsightsのアナリストLinley Gwennap氏は述べている。また、米国政府が国内製造支援に拠出する527億ドル(約7兆2000億円)の補助金が実際に提供されるのは、2023年になる見通しだ。

パッケージング技術によって、Intelはかつての主導的地位を取り戻せるかもしれない。

Intelの共同創設者であるGordon Moore氏はかつて、大きなシリコンの塊からチップを作ることがもはや意味をなさなくなる「審判の日」が来ると予測した。「ムーアの法則」を論じて大きな影響力をもたらすことになった論文に、同氏は次のように記している。「個別にパッケージングされ、相互に接続された複数の小さな機能から大規模なシステムを構築する方が経済的であることが、いずれ証明されるかもしれない」

Intelはパッケージングに関して、主に2つのアプローチを採用している。

1つ目は「EMIB」(組み込みマルチダイ相互接続ブリッジ)で、横に並べた2つの「チップレット」を下から小さなブリッジで接続するというものだ。このアプローチはPonte Vecchioで利用されているほか、次期サーバー向けプロセッサー「Sapphire Rapids」にも採用されている。

2つ目は「Foveros」で、パンケーキを積み重ねるように複数のチップレットを垂直方向に結合する。このアプローチで製造されているMeteor Lakeでは、4つのチップレットが、通信リンクを提供するインターポーザー上に置かれている。

このFoverosは、Meteor Lakeの後継でCPU(中央処理装置)の回路がアップグレードされる「Arrow Lake」にとっても重要な技術だ。また、その後に登場する「Lunar Lake」にも採用される。Lunar Lakeは、消費電力が極めて低いノートPC向けのチップで、チップレットの構成が刷新される予定だ。Phelps氏によると、Arrow LakeとLunar Lakeはいずれも「2024年中に投入」されるようだ。

EMIBとFoverosはどちらも、ムーアの法則に従ったトランジスター数の増加を維持するのに役立つものだ。例えば、スーパーコンピューター向けチップであるPonte Vecchioの場合、トランジスターの数は1000億を超えている。

チップレットのパッケージングによって得られる大きなメリットの1つは、チップ設計者が複数のプロセッサーコンポーネントを組み合わせられるようになることだ。パフォーマンスが最も重視されるチップレットは、高価な最新世代の製造プロセスで生産し、それほど重要性が高くない部品は、すでに実績のある旧式の安価なプロセスで生産するといったことが可能になる。

「(設計者が)より革新的な技術に集中できるようになり、基本的な作業に時間を費やすことがなくなる」と、Kanter氏は語った。

また、チップレットによって、Intelの製造プロセスにおける問題が緩和される。Meteor Lakeでは、4つのデータ処理用チップレットの3つが、最大のライバルであるTSMCによって製造されている。Intelはすべてのコンポーネントを設計しているが、製造しているのはCPUコアを持つチップレットだけだ。

さらに、チップレットのおかげで、設計者が新しい製造プロセスをより迅速に採用できるようになる。全種類のトランジスターが、より高度なフォトリソグラフィー工程に更新されるまで待つ必要がないため、チップメーカーは、パフォーマンスが最も重視されるタスクにのみ新しいプロセスを採用できるようになる。

この記事は海外Red Ventures発の記事を朝日インタラクティブが日本向けに編集したものです。