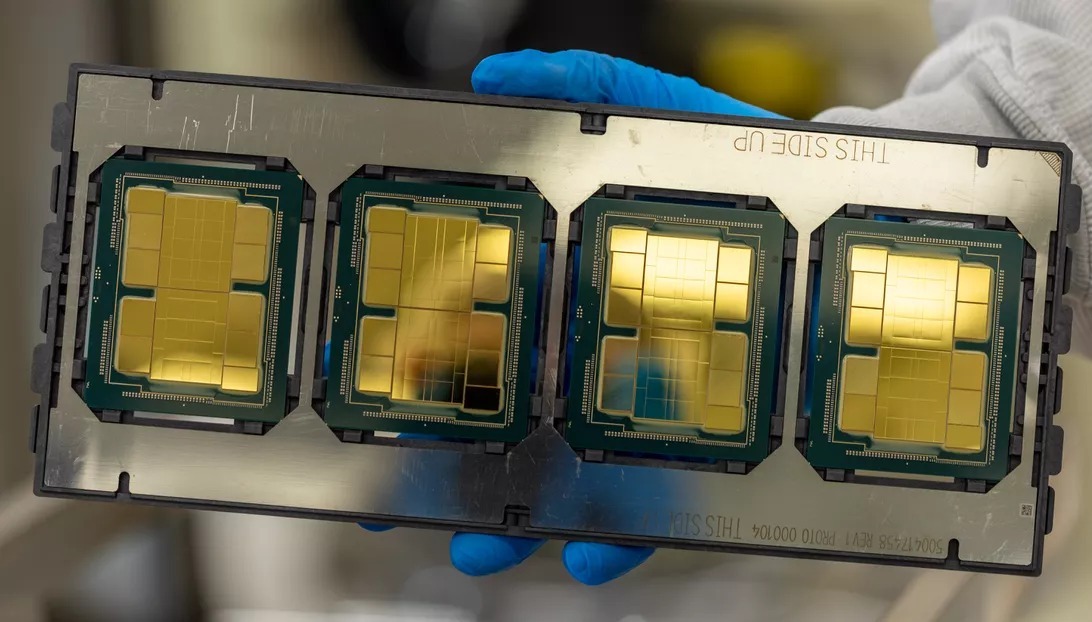

Intelは米国時間1月19日、2025年までに半導体製造のリーダーとしての地位を取り戻す取り組みの一環として、オランダのASMLが手がける次世代型半導体製造機器を他社に先駆けて発注したと発表した。Intelが今回発注した「Twinscan EXE:5200」という機器は2024年に納品され、2025年に運用が開始される予定だ。

提供:Stephen Shankland/CNET

ASMLは、1台あたりの平均価格が3億4000万ドル(約390億円)にもなるこういった機器が、プロセッサーの進歩に不可欠なものになると予想している。半導体の小型化はますます難しくなってきているが、スマートフォンやPC、データセンターにおける進歩を柱とするテクノロジー大手にとってその追求は極めて重要となっている。

Intelは数十年にわたって半導体製造分野をリードしており、半導体の処理能力をさらに高めるための回路の微細化に絶えず取り組んできた。GlobalFoundriesやIBMといった競合他社が最先端技術の追求という競争から降りた一方、Intelは製造上の問題を抱え、Taiwan Semiconductor Manufacturing(TSMC)やサムスンに後れを取るようになった。

半導体の小型化における中心課題は、シリコンウエハー上に今まで以上に細かく回路を刻み込むというものだ。ASMLは、このプロセスにおける主要な部分を取り扱う「フォトリソグラフィー」と呼ばれる機器を製造している。フォトリソグラフィーという言葉は、「フォト」(光)による「リソグラフィー」(石に刻むこと)に由来している。サムスンとTSMCの両社は、このプロセスで使用する光の波長をより短い極端紫外線(EUV)へと移行済みであるため、多くの工程を経てプロセッサー上に形成するトランジスターやワイヤリングのパターンをより微細なかたちで刻み込めるようになっている。

IntelはEUVリソグラフィーの導入に出遅れたものの、エンジニアらを再び率いることになった最高経営責任者(CEO)のPat Gelsinger氏はこの取り組みを加速させようと力を注いでいる。同氏は、さらに微細なパターンを刻み込むための高NA(開口数)を有する、より先進的なEUVツールを他社に先駆けて導入すると述べていた。ASMLは18日に初の注文を受けたと発表し、19日にIntelがその発注者であることを明らかにした。

Intelはこのツールの価格についてコメントを控えた。

他社に先駆けたとしても、そのこと自体が成功を保証してくれるわけではない。半導体の製造にはさまざまな側面があり、新たな製造プロセスでの量産にこぎ着けるには何年もかかる上、Intelは第1世代のEUVで出遅れている。Intelは同社初のEUV半導体を2022年に、そして同社初の高NA EUV半導体を2025年に販売開始したいと考えている。

プロセッサーメーカーは、世界的なチップ不足や、プロセッサーが生活のあらゆる場に浸透していることなどから、ファブと呼ばれるチップのファブリケーション施設に巨額の投資をしている。

この記事は海外Red Ventures発の記事を朝日インタラクティブが日本向けに編集したものです。