理化学研究所(理研)と富士通は6月21日、共同開発を進めているスーパーコンピュータ「京」の後継機(ポスト「京」)において中核となるCPUの試作チップを完成させたと発表した。ポスト「京」は2021年ごろの完成を予定している。

完成したCPUの試作チップは、富士通が英Armとの協業で策定したハイパフォーマンスコンピューティング向けにベクトル処理能力を拡張するArm v8-Aアーキテクチャの拡張命令セットアーキテクチャを採用する。CPUコアは、計算ノードで48コア(および2アシスタントコア)、I/O兼計算ノードで 48コア(および4アシスタントコア)で構成される。

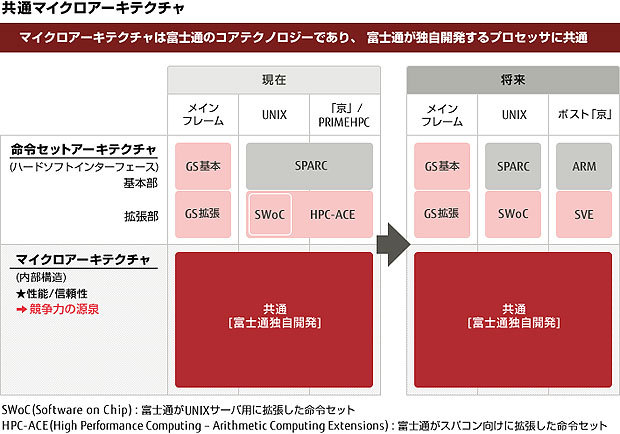

富士通では、同社のマイクロアーキテクチャも継承することで、「高性能積層メモリと相まったメモリバンド幅と演算性能を備え、アプリケーションの実行性能が高いレベル」で実現できるよう最適化を図り、省電力設計と電力制御機能によって、低消費電力でも高い性能を実現すると説明する。

ポスト「京」は、2012年から稼働する「京」の後継システムとして、2014年10月に設計がスタート。試作と詳細設計を進めている段階にあり、今回のCPUの試作チップは既に初期動作を確認済み。「システム開発における重要なマイルストーンを順調にクリアした」(富士通)としている。

また、言語仕様とマイクロアーキテクチャに継続性が確保され、「京」のプログラム資産をリコンパイルすることにより、ポスト「京」へ確実に移行と性能確保が可能になるという。理研が開発するシステムソフトウェアの「McKernel」「XcalableMP」「FDPS(Framework for Developing Particle Simulator)」も引き続き利用できるとする。

ポスト「京」に至るマイクロアーキテクチャ(出典:富士通)

ポスト「京」は、現行の「京」に比べて最大で100倍のアプリケーション実行性能と30~40Mワットの消費電力が目標とされている。