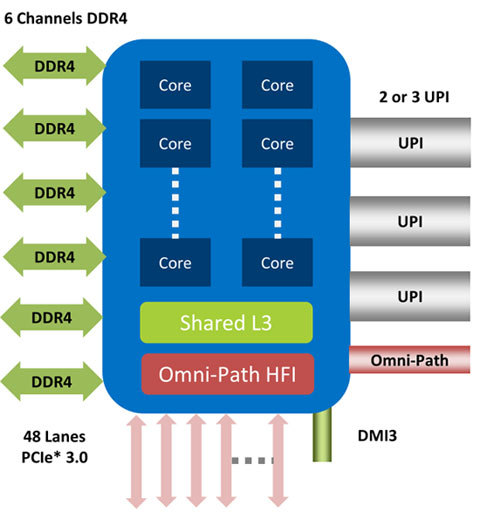

「Intel Xeon Scalable Processor Family」(Xeon Scalable)は、1プロセッサに6チャンネルのDDR4対応メモリインターフェースが用意されている。1チャンネルあたり2本のDIMMが使えるため、1プロセッサあたりでは最大12本のDIMMを使用できる。これにより、最大768GBもの大容量メインメモリがサポートされる(64GBのDDRメモリを使用した場合)。

Xeon Scalableは、プロセッサが直接DDR4メモリをドライブする。Xeon E7のようにバッファなどがないため、DDR4の高速メモリを直接利用できる(米Intelの発表資料より。以下明記が無い場合は同じ)

また、Xeon Scalableの特別バージョン(最後に「M」という型番が付く製品)は、1.5TBのメモリ容量をサポートする。これは、メモリのチャンネル数が増えるのではなく、128GBのメモリをサポートするというテストを行い、動作を保証した製品ということだ。サポートされているDDR4メモリは、最大2666MHzをサポートしている。ただし、モデルによってサポートしている最大メモリスピードが制限されている。

Xeon E7は、多数のメモリを接続するために、SMI(Scalable Memory Interconnect)にSMBチップ(Scalable Memory Buffer)を接続して、最大24本のDIMMを接続していた。しかし、この方式ではSMBなどバッファ部分が多くなり、高速なメモリを使用できなかった。そこで、直接プロセッサがメモリをドライブする方式に変更され、高速メモリをサーバでも使用できるようになった。

最近は、データベースもデータをメモリ上に展開して、高速に処理するインメモリデータベースが普及し始めている。このような用途に対応するためにも、高速でアクセスできるメモリは非常に重要だ。さらに、高速なメモリを大容量サポートしていることも重要となる。

メモリの動作クロックは、サーバ全体のパフォーマンスにも関わるため、高速なメモリを使用できることで、サーバ全体のパフォーマンスを引き上げる。

Xeon Scalableでは、8ソケット、4ソケット、2ソケットのサーバを構成できるようになっている(最上位モデルが8ソケットをサポート、ミドルモデルが4/2ソケットをサポート、最下位モデルが2ソケットをサポート)。ソケット間のインターコネクトとして、以前のQPI(Quick Path Interconnect)からUPI(Ultra Path Interconnect)に変更されている。QPIは最大9.6GT/sだったが、UPIは最大10.4GT/sにアップしている。大きな変化ではないが、今後UPIもバージョンアップされるごとにスピードアップしていくことになる。ある意味UPIに変更されたことで、今後の基盤ができ上がったといえる。

また、Xeon ScalableのモデルによってUPIのサポートが2本もしくは3本に分かれている。UPIのサポートが3本のモデルは8/4ソケットをサポートし、UPIが2本のモデルは2ソケットをサポートする。

Xeon Scalableでは、プロセッサが直接48レーンのPCIe3.0インターフェースをサポートしている。このため、周辺チップ経由での接続に比べてボトルネックになる部分がなく、周辺カードのパフォーマンスを最も生かすことができる。

さらに、48レーンのPCIe3.0インターフェースによって、人工知能や機械学習などで注目を浴びているGPGPUを最大3台接続することができる。また、高速なアクセスを可能にするフラッシュストレージのNVMe SSD(PCIe Gen3×4レーン)を最大12台まで接続できる。ただ、全てをGPGPUやNVMe SSDでPCIeインターフェースに使用するわけではないため、GPGPUは最大2台、NVMe SSDは8台ぐらいが標準的な構成になるだろう。