本連載「ハードから読み解くITトレンド放談」では、ハードウェアの最新動向からITシステムのトレンドと未来を読み解いていく。

Xeon E7/E5の違い

前回解説したBroadwellコアの特徴を踏まえ、今回はメインとなるXeon E7とE5を掘り下げながらサーバシステムの今後をひもといてみたい。

Xeon E7とE5の大きな違いは、メモリインタフェースが異なることと、チップセットと組み合わせてサポートされるソケット数(プロセッサ数)の差になる。細かいところでは、システムダウンが許されないワークロードを動かすE7に、さまざまな耐障害性やOSと連携してハードウェアのトラブルを回避する手立てが用意されている。

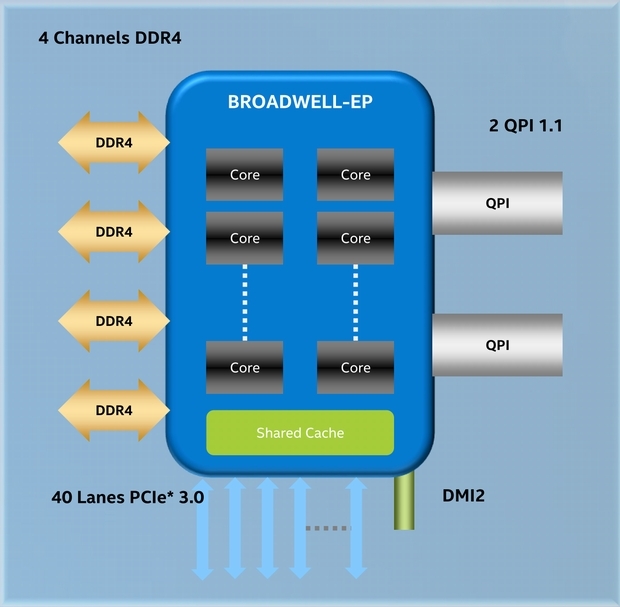

Xeon E5 V4は、メモリにDDR4を採用し、メモリチャンネルは4本となっている。1本のメモリチャンネルに最大3本のDIMMメモリを搭載できる。ただし、デスクトッププロセッサと同じように1本のメモリチャンネルに3本のDIMMメモリを搭載した場合は、30%ほどメモリの動作スピードが低下する。このため、メモリの動作スピードを落としても搭載メモリ容量を増やすか、もしくは少ない搭載メモリ容量でメモリの動作スピードを高めるのかを選択する必要がある(Xeon E5 V3の最大メモリは1.54TBとなる)。

Xeon E5 V4のブロック図(IntelのXeon E5 V4発表資料より、以下同)

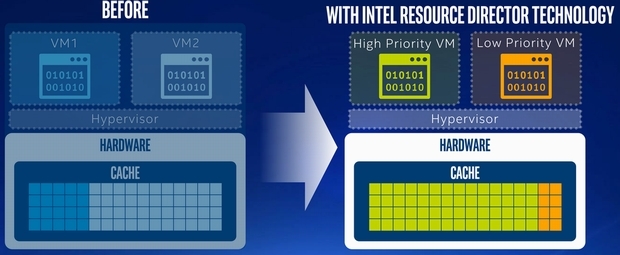

Xeon E5 V4で追加された「Resource Director Technology」。仮想化使用時に、プライオリティの高い仮想マシンにキャッシュを優先的に割りあてる

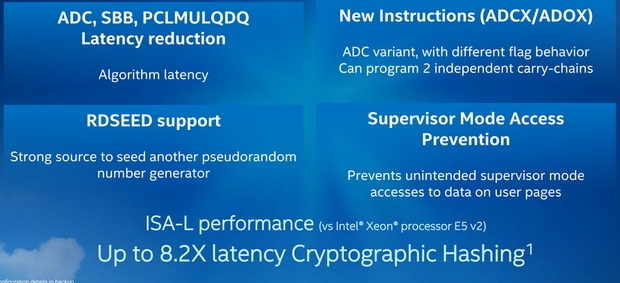

Xeon E5 V4で追加された機能

最近はDRAM容量がアップしているため、コストアップになるが、64GB DDR4メモリを使用すれば、1ソケットサーバでは768GBとなる。一般的には、メモリの動作周波数がサーバ全体のパフォーマンスを左右する。このため、1チャンネル2本のDIMMメモリで、1プロセッサでは8本のDIMMメモリを使用しているようだ。

一方のXeon E7 V4では、プロセッサから出るメモリチャンネルは4本だが、各メモリチャンネルに「Intel Scalable Memory Buffer」(SMI)を使用することで、SMI経由ではメモリチャンネルを2本にできる。つまりSMIを使えば、Xeon E7 V4では、最大8本のメモリチャンネルを持てる。1本のメモリチャンネルで3本のDIMMメモリを搭載できるため、Xeon E7 V4は最大24本のDIMMメモリを搭載できるというわけだ。メモリの動作周波数はXeon E5 V4より低下するが、最大3.07TBもの大容量メモリを搭載できるようになっている。

Xeon E7 V4では、Broadwellコアが持つ機能にプラスして、「Cluster On The Die」(CoD)という機能が用意されている。

CoDは、1つのプロセッサを仮想的に分割し、複数の仮想プロセッサとして見せることができる(電源投入後のファームウェアで動作を決定する)。プロセッサを仮想的に分割するとはいえ、仮想化(ハイパーバイザ)などを使ったものではなく、ハードウェアレベルで仮想的に分割する。

これは、Xeon E7 V4のキャッシュメモリなどの大容量化に伴って、コアによっては、特定のキャッシュメモリ(Last Level Cache=LLC)にアクセスするのに時間がかかるようになったことから、ハードウェアレベルで仮想的にプロセッサを分割した方が便利な場合があるためだ。ただし、CoDでプロセッサを仮想的に分割した場合、メモリやI/Oなどは、分割した仮想プロセッサに接続されているモノにアクセスする。つまり、周辺を含めて1つのプロセッサを分割するととらえた方がいいだろう。